# Chapter 2 General Overview of Pipeline Analog-to-Digital Converters

**Abstract** This chapter provides a general background for the work carried out in this book. Therefore, its purpose is to cover all aspects of the developed work. First, some A/D converter (ADC) architectures will be briefly described. The common element of these architectures is the use of the multiplying-DAC (MDAC) circuit as their principal block. Advantages and limitations of the architectures will also be given. The MDAC circuit is one of the key elements of this book. Given that this work presents a prototype of a pipeline ADC, it is important to describe each of its building blocks. Besides detailing the function and importance of each block, related errors and performance limiting aspects will also be given. After the description of the pipeline converter sub-blocks, various static and dynamic performance parameters, and metrics that characterise ADCs are given. It will be the objective here to explain the parameters that fundamentally dictate the performance of ADCs. Finally, the chapter is completed with a state-of-the-art of medium-low resolution high-speed pipeline ADCs. Besides this overview, surveys of two key building blocks, namely, two-stage amplifiers and reference voltage circuits (in the context of A/D conversion), which deserved special attention in this work, are also presented.

# 2.1 MDAC-Based Analog-to-Digital Converter Architectures

There are many architectures of A/D converters, each with their own set of characteristics and capabilities to be used in different applications. Well known architectures are Full-Flash (or Parallel), Two-Step, Sub-Ranging, Folding, Integrating, Successive Approximation (SA), Algorithmic, Pipeline, Sigma-Delta modulators, and Time-to-Digital. It is also possible to find numerous combinations of the various existing topologies, such as: time-interleaving can be used as a means of increasing the sampling frequency (conversion rate) by arranging various converters of the same type in parallel; it is very frequent to find interpolation associated with flash and folding converters; the two-step topology can employ either flash or SA architecture in each

step; the pipeline and algorithmic topologies usually employ flash converters in each step, etc.

Part of the work carried out in this book implements an ADC topology that employs MDAC circuits, consequently, the only converter topologies of interest, of the ones mentioned above, are those that use MDAC circuits as a means of obtaining a residue with amplification (i.e., simultaneous DAC, subtraction, and residue amplification functions). With this in mind the only architectures that will be discussed are the Two-Step (flash), the multi-step Algorithmic, and the Pipeline, targeting higher conversion rates. The time-interleaving technique will also be briefly described.

## 2.1.1 Two-Step Flash ADC

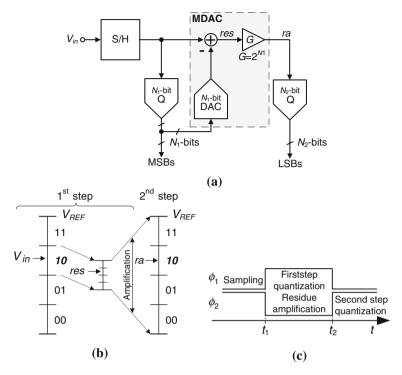

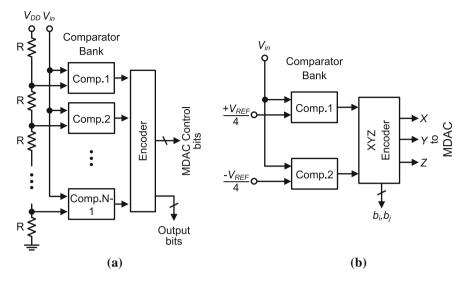

The Two-Step Flash architecture evolved from the Full-Flash converter. One of the main drawbacks of the latter is the number of necessary comparators, given by  $N_{comp.} = 2^N - 1$ , which scales exponentially with the resolution of the converter (N), making it, in some cases, impractical to implement due to the necessary die area. The Two-Step Flash topology alleviates the number of necessary comparators by quantizing the input in two steps, hence its name, as shown in Fig. 2.1a. The effective reduction factor in the number of comparators when compared to the Full-Flash ADC, is exponentially proportional to the converter's resolution, and is approximately given by  $12^{\frac{N}{2}-1}$ . In other words, the higher the resolution the more area efficient it becomes to use a Two-Step topology.

As shown in Fig. 2.1a, each step (or stage) is composed of a quantizer, with a resolution  $(N_1 \text{ and } N_2)$  inferior to the resolution (N) of the entire converter, thus requiring less reference voltages and comparators, and consequently, occupying less die area. Between the two steps an amplified residue voltage needs to be generated, which is achieved with a DAC, a subtraction operation block and a gain block. These three blocks constitute an MDAC circuit. The principle of operation is as follows: the input is sampled by the first quantizer during the sampling phase. During the residue amplification phase, the first quantizer decides the most significant bits (MSBs), which are then used to reconstruct a voltage (using the DAC), that is subtracted from the original sampled input and then amplified (by  $2^{N_1}$ ) to create an amplified residue voltage. Still during this phase, the second quantizer samples this residue. The objective of the amplification is to restore the residue to the full voltage range of the converter, thus facilitating the implementation of the second quantizer (Fig. 2.1b), or eventually, reusing the same quantizer in a cyclic way. During the final phase, the second quantizer (of resolution  $N_2$ ) quantizes the residue to obtain the least significant bits (LSBs). The final digital output is assembled using digital logic, by adding the MSBs together with the LSBs.

Basically, this topology simplifies the quantization, by trading comparators with time. The Full-Flash converter achieves a quantization in two clock phases (one clock cycle), while the Two-Step needs at least three phases, i.e., one and a half clock

<sup>&</sup>lt;sup>1</sup> Assuming that the same number of bits is extracted in both quantization steps, i.e.  $N_1 = N_2 = N/2$ .

Fig. 2.1 The Two-Step A/D converter: a Block diagram. b Example of residue amplification. c Timing diagram

cycles (Fig. 2.1c). Although the throughput may be similar to that of the Full-Flash converter (one digital output per clock cycle), the Two-Step has higher latency.<sup>2</sup> If  $N_1$  is made equal to  $N_2$ , then only one quantizer needs to be designed and, therefore, both quantizers may use the same reference voltages. The latter is also made possible by using a residue amplification gain of  $2^{N_1}$ . The above assumptions consider that no digital redundancy is used.

If more steps (or stages) are added to the converter to simplify its implementation and relax the requirements of each step, which would eventually lead to a minimum resolution per step (N = 1), the resulting A/D architecture would be the Pipeline.

# 2.1.2 Pipeline ADC

The Pipeline converter's operation is basically the same as that of the Two-Step Flash. Each stage is responsible for quantizing  $N_j$ -bits,  $j=1,2,\ldots,K$  ( $N_j < N$ ) and generating an amplified residue for further quantization (performed by subsequent

<sup>&</sup>lt;sup>2</sup> Latency is the number of initial clock cycles to produce the first digital output.

stages). However, the first stage does not have to wait for the residue of a specific sample to reach the end of the pipeline, to conclude its quantization. As soon as the first stage has performed its task, it may quantize the next input sample. This holds for all stages, which means that at any given time, except at the beginning when the converter starts its operation, all stages are processing data. Thus, the throughput of the Pipeline converter may be similar to that of the Full-Flash ADC, but its latency is high, even higher than that of the Two-Step Flash converter. The more stages there are in the pipeline chain, the higher the latency will be.

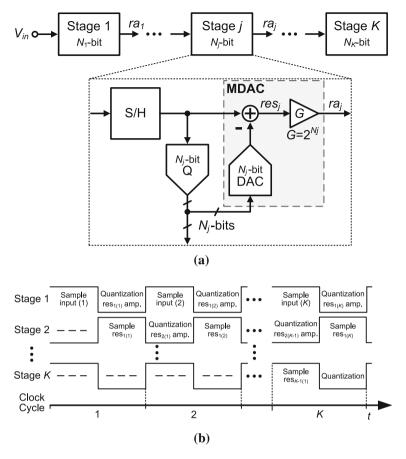

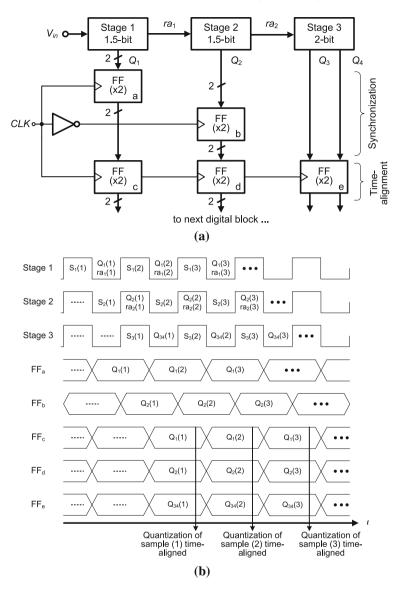

As shown in Fig. 2.2a, each stage of a Pipeline converter is composed of a flash quantizer and an MDAC. The flash quantizer quantizes the input sample (or residue) and generates  $N_j$  bits. In the literature it is common to find 1 to 4 bit quantizers (in half-bit intervals, 1.5-bit, 2.5-bit, etc.), the most common being 1.5-bit. The MDAC is responsible for reconstructing a residue voltage, determined by the  $N_j$  bits of the quantizer, subtracting it from the stage's input voltage and amplifying the result, to generate the residue voltage. This voltage is then held and passed onto the next stage where the stage's operation is repeated. The amplification of the residue, by  $2^{N_j}$ , is justified for increasing its dynamic range to the full scale range of the converter, thus facilitating the implementation of subsequent quantizers. Each stage's operation is completed in two phases (one clock cycle): the first for sampling and quantizing, and the second for residue amplification (see the timing diagram of Fig. 2.2b).

Normally, all pipeline stages are designed with the same resolution to simplify the converter's layout and implementation, but, design trade-offs may determine that each stage have different resolutions. It is usual to find the first stage with a higher resolution. Another important reason for all stages to be equal (in resolution) is that the reference voltages are the same for all quantizers and DAC functions.

What concerns digital logic, the Pipeline converter employs digital synchronization logic to align (over time) all bits before producing the final digital output word. Aside from synchronizing, these converters usually employ digital correction, which corrects for nonidealities in the flash quantizers [97]. The Two-Step Flash converter, described above, may also employ digital correction logic. These digital blocks are detailed further on in this chapter.

# 2.1.3 Multi-Step Algorithmic ADC

The Algorithmic (or Cyclic) converter, as the name indicates, quantizes the input sample in an algorithmic or repetitive manner. Its principle of operation is basically the same as that of the Pipeline converter, in that an input is sampled, quantized, and a residue is amplified, and then the quantization and residue amplification process is repeated by subsequent stages. The main difference with the Algorithmic converter is that the conversion algorithm (sampling, quantization, and residue amplification) is repeated in the same physical space (reutilizing the same circuits) or area, while the Pipeline ADC repeats its operation over more area. In other words, the Algorithmic converter trades space for time, which means it has a longer conversion cycle.

**Fig. 2.2** The Pipeline A/D converter: **a** Block diagram of a stage, exemplifying its building blocks. **b** Timing diagram

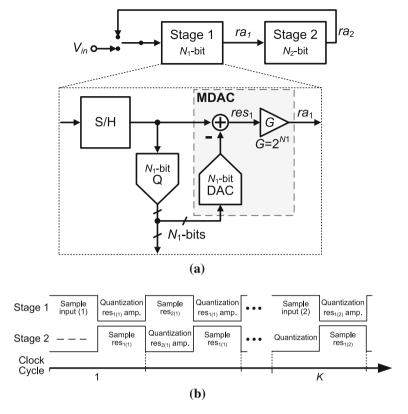

The converter has a minimum number of stages (usually two), where the residue repeatedly passes through each stage, successively generating output bits, from the MSB to the LSB, as shown in Fig. 2.3a. After the LSB is generated, the process starts over again with a new sample.

The principle of operation is as follows: the input voltage is sampled by the first stage. It is then quantized to generate the MSBs. These bits are used to reconstruct a voltage (using a DAC and reference voltages) that is subtracted from the input voltage generating the residue voltage. This residue is then amplified (and held) to the full scale range of the converter and sampled by the second stage. This process repeats itself between the first and second stages until the LSB is generated. At this point a full digital output is ready, while the converter is sampling the next input sample (Fig. 2.3b).

Fig. 2.3 The Algorithmic A/D converter: a Block diagram. b Timing diagram

Unlike the Pipeline, this converter is unable to process more than one sample at any given time, thus a converter of resolution N needs N+1 clock cycles to quantize a single input sample. Compared to the Pipeline ADC, this converter's throughput is much lower, but has the same latency. It trades throughput with die area and facilitates layout and implementation due to the number of necessary blocks, which are much less than that used in a Pipeline converter.

The Algorithmic architecture must employ digital circuitry to hold and align the digital outputs of each stage before producing the final output word, and it usually employs digital correction logic.

In order to increase the throughput, the time-interleaved technique may be employed.

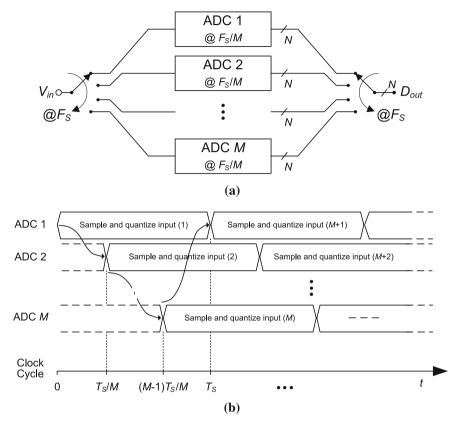

Fig. 2.4 Time-interleaving of A/D converters: a Block diagram. b Timing diagram

## 2.1.4 Time-Interleaving ADCs

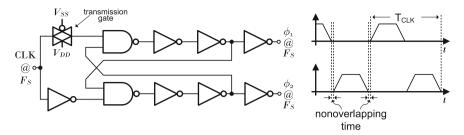

Time-Interleaving [11] is a technique used to increase the throughput or conversion rate of a converter. This technique may be applied to all A/D converter topologies. It consists of using an array of M parallel converters multiplexed at the input and at the output as shown in Fig. 2.4a. Each converter operates at a conversion rate  $F_{S/M}$  (where  $F_S$  is total conversion rate), making it easier to implement. The analog input multiplexer, adequately timed, is responsible for attributing an input sample to each of the converters over time, when it reaches the last converter in the array it starts over again. The digital output multiplexer guarantees that the timing sequence of digital outputs are in accordance with the sampled inputs. Each converter added to the array inevitably increases the die area and the power consumption of the overall A/D conversion system. The timing diagram of operation is shown in Fig. 2.4b.

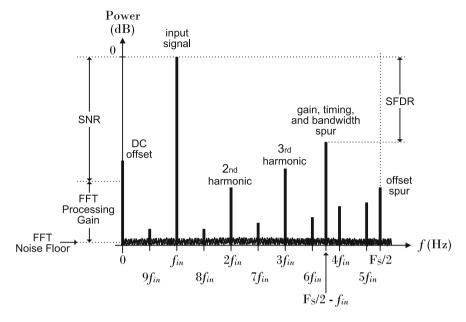

Besides the limitations produced by each unit (multiplexed) ADC, the timeinterleaved technique introduces its own limitations. These have mainly to do with mismatches between the various unit ADCs that compose the converter [11, 39, 80, 91, 133, 172]. This topology is very sensitive to mismatches in the offset, gain, timing, and bandwidth of each unit ADC. All these extra errors (inherent to time-interleaving) cause a degradation of the converter's signal-to-noise ratio (SNR). No matter how large the error of a unit ADC is, as long as all other unit ADCs have the same error magnitude, no mismatch will exist. A brief description of these errors is given next and Table 2.1 presents a summary of the effects of time-interleaving mismatches [11, 39, 80, 91, 133, 172]. For this discussion, a two-channel time-interleaved ADC will be used as an illustrative example.

- Offset mismatch contributes with a component at DC (frequency, f = 0) in the output spectrum, which is already expected because all ADCs have an offset, but, it also adds a spurious tone at half the sampling frequency  $(F_S/2)$ . The spectral locations and the magnitude of these components are independent of input signal amplitude and frequency.

- Gain mismatch contributes with a spurious tone at half the sampling frequency minus the input frequency  $(F_S/2 f_{in})$ , thus its spectral location is dependent on the input signal frequency. The magnitude of the spurious tone is only dependent on the amplitude of the signal. The magnitude of the input signal is affected by this mismatch.

- Timing mismatch is due to variations in the sampling instant of each unit ADC, in other words, differences in the relative time between samples taken. This mismatch is similar to gain mismatch in the sense that it contributes with spurious tones at the same spectral locations  $(F_S/2 f_{in})$ , but, the magnitude is dependent on the amplitude and the frequency of the signal. As with gain mismatch, timing mismatch affects the magnitude of the input signal.

- Bandwidth mismatch is due to differences in the sampling networks of each unit ADC. If each unit ADC has a dedicated sample-and-hold (S/H), and if each S/H has a different bandwidth, then bandwidth mismatch will affect the performance of the overall time-interleaved ADC [39, 91]. This mismatch adds similar contributions to that of gain and timing mismatches. The main differences are that the gain part of the bandwidth mismatch is now dependent on the input signal frequency and the timing part has a nonlinear dependency with the input signal frequency.

# 2.2 Building Blocks of Pipeline Analog-to-Digital Converters

The objective of this section is to briefly overview each of the constituent blocks of a Pipeline A/D converter. Besides an overview, errors related to each block will also be given. Various references are given throughout the section for a more detailed coverage and further reading. Note that, not all the blocks described below are necessary to build a Pipeline ADC. For example, the sample-and-hold (S/H) and decimation blocks are not strictly necessary. It should be equally noted that the blocks described

**Table 2.1** Magnitude and spectral location of spurious tones due to mismatches and their effect on the signal  $(A_{in} \sin(2\pi f_{in}))$  component for a two-channel time-interleaved ADC. The offset and gain mismatches are given by  $o_i$  and  $g_i$  respectively (i=1,2). The relative timing mismatch is given by  $r_i = \Delta t_i/T_S$ , where  $\Delta t_i$  is the absolute timing mismatch and  $T_S (= 1/F_S)$  is the sampling period

| Mismatch type | Signal component (Magnitude)               | Spurious component<br>(Spectral location)<br>(Magnitude)                                 |  |  |

|---------------|--------------------------------------------|------------------------------------------------------------------------------------------|--|--|

| Offset        | _                                          | DC $F_S/2$                                                                               |  |  |

| Gain          | $A_{in} \frac{g_1 + g_2}{4}$               | $ \frac{o_1+o_2}{2} \qquad \frac{o_1-o_2}{2}  F_S/2 - f_{in}  A_{in} \frac{g_1-g_2}{4} $ |  |  |

| Timing        | $A_{in}\cos(2\pi f_{in}\frac{r_1-r_2}{2})$ | $F_S/2 - f_{in}$                                                                         |  |  |

| Bandwidth     | see [91]                                   | $A_{in} \sin(2\pi f_{in} \frac{r_2 - r_1}{2})$ $F_S/2 - f_{in}$ see [91]                 |  |  |

below are generic, in the sense that they are found in most Pipeline ADCs. In recent developments some of these blocks have been substituted for more efficient ones and some have been eliminated (mostly for power and/or area savings).

## 2.2.1 Sample-and-Hold

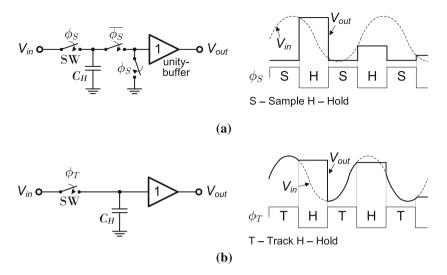

The sample-and-hold (S/H) block is found at the very beginning of the converter. Its objective is to discretise, in time, i.e., to sample the input and hold the sampled input for the subsequent block to process it. The S/H converts a continuous-time signal into a discrete-time signal (the signal is still continuous in amplitude). Another circuit with similar functions is a track-and-hold (T/H), where the main difference to a S/H is that the output of the T/H tracks (follows) the input, then samples, and finally holds the sample. A simple version of a S/H and a T/H are shown in Fig. 2.5 with their respective timing diagram.

S/H circuits operate in two phases, the sampling and the holding phase, as shown in Fig. 2.5a. During the sampling phase, the switch ( $\phi_S$ ) is closed and the capacitor is charged to the input voltage. When the switch is opened, the input is sampled, and because the charge on the capacitor can not be destroyed, the sampled voltage is held on the capacitor. At this moment, the held voltage can only be sensed by a high input impedance block such as an amplifier (unity-buffer in this case).

There are numerous errors associated to sampling and holding an input signal [9, 84, 135]. Some are mentioned below:

Fig. 2.5 Simple versions of (a) S/H and (b) T/H, with output buffer and output waveform

- Finite sampling bandwidth if the input signal's frequency is higher than the sampling bandwidth  $(f_{-3 \, dB} = 1/(2\pi \, R_{SW} C_H))$ , an output signal voltage with a phase difference is sampled.

- **Acquisition time** is the time it takes the amplifier (buffer) to settle. This error is associated with amplifiers which will be explained further on.

- Sampling uncertainty (aperture error) is the time uncertainty at the moment of sampling. This error has two possible origins: a long rise or fall time, or a sampling instant that changes from period to period. This error is particularly problematic in the presence of high frequency signals.

- Sampling pedestal is the error voltage added to the sampled voltage caused by the switch while it is turning off. This extra voltage is due to channel charge injection and clock feed-through. This error is particularly problematic when the error voltage is signal dependent, which adds distortion.

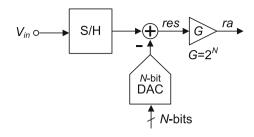

# 2.2.2 Multiplying-DAC

As seen in the previous section, the MDAC is a circuit which performs numerous functions. These functions include sampling the input signal (or residue voltage from a previous stage), reconstructing a voltage using a DAC, obtaining a residue (subtraction of the reconstructed voltage from the stage's sampled voltage), performing a gain to amplify the residue, and finally holding the amplified residue for the next stage. The block diagram of a generic MDAC is shown Fig. 2.6. Normally, a switched-capacitor (SC) network is employed to accomplish all these functions. Sampling is

**Fig. 2.6** Block diagram of a generic *N*-bit MDAC

**Fig. 2.7** Closed-loop switched-capacitor opamp-based 1.5-bit MDAC

achieved by means of switches and capacitors, similar to that shown in the previous subsection. The MDAC employs an operational amplifier (opamp) with a capacitive feedback network (closed-loop) to provide the DAC, subtraction, and amplification functions.

In the literature it is possible to find various techniques of implementing the MDAC function, either in open or closed-loop, such as, closed-loop switched-capacitor techniques, switched-current techniques [103], open-loop amplification [114], dynamic source follower amplification [76], MOS parametric amplification [123], and the substitution of the opamp for a comparator based circuit [15], among others. Each technique has its own advantages and limitations, not discussed here.

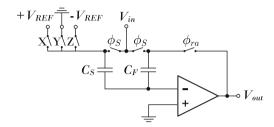

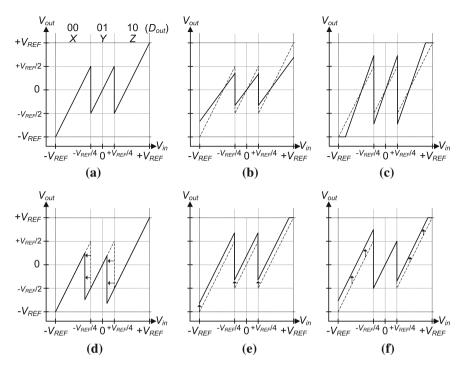

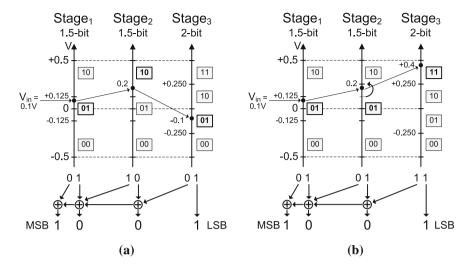

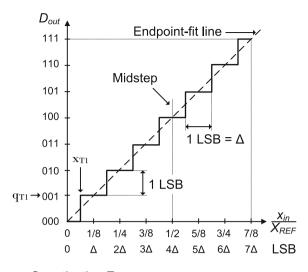

To understand the principle of operation of an MDAC circuit, a simple closed-loop switched-capacitor opamp-based 1.5-bit MDAC is used, as shown Fig. 2.7 (single-ended shown for simplicity) [98]. This resolution MDAC (1.5-bit) is chosen because it is one of the most widely used of all implemented stage resolutions. The input-output transfer characteristic is shown in Fig. 2.8a (ideal case). This characteristic can be described by the following expression

$$V_{out} = 2V_{in} + B \cdot V_{REF}, \tag{2.1}$$

where B represents the bit decisions made by the local quantizer (represented in Fig. 2.7 by X, Y, or Z which represent B = +1, B = 0, and B = -1, respectively) and  $V_{REF}$  represents the converters reference voltage. Equation 2.1 shows that the MDAC has a gain component  $(2V_{In})$  and a reference shifting component  $(B \cdot V_{REF})$ .

Circuit operation is as follows: during  $\phi_S$  the input  $(V_{in})$  is sampled onto capacitors  $C_S$  and  $C_F$ . During the residue amplification phase  $(\phi_{ra})$ ,  $C_F$  is put in the opamp's feedback loop, and, due to charge conservation, the charge on  $C_S$  is transferred to

**Fig. 2.8** Input—Output characteristics of the 1.5-bit MDAC and the effects of errors (*dashed line* represents the ideal situation): **a** Ideal. **b** Gain error: gain < 2. **c** Gain error: gain > 2. **d** Offset of the quantizer decision levels. **e** Offset in the MDAC due to charge injection or offset of the opamp. **f** DAC nonlinearity

$C_F$ . The amount of transferred charge depends on the quantizer's decision (X, Y, or Z). If Y is high, i.e., if the Y switch is closed, the sampled input charge on  $C_S$  is transferred to  $C_F$ . In this case the output  $(V_{out})$  will simply be  $2V_{in}$  (parameter B of Eq. 2.1 is 0). If X or Z is enabled, then there will respectively be a charge addition or subtraction on  $C_S$  and the resultant charge transferred to  $C_F$ . In this single-ended version example, the DAC is only composed of capacitor  $C_S$ .

The limiting factors of closed-loop SC-MDAC circuits are given next. To aid the enumeration of these factors, the example of the 1.5-bit MDAC will be used as well as its transfer characteristics shown in Fig. 2.8.

- Gain error caused by capacitor mismatch (between  $C_S$  and  $C_F$ ) and finite opamp DC gain [97, 102, 156]. Slopes of the characteristic vary from the ideal value of 2. See Fig. 2.8b, c.

- Offset errors can be caused by offset of the quantizer decision levels (Fig. 2.8d), by charge injection [86], or by opamp offset in the MDAC (Fig. 2.8e). Offset errors are of minor importance given that most errors can be corrected by the digital correction logic [97].

- **Nonlinearity errors** caused by DAC capacitor mismatch and nonlinearity errors present in the opamp [102] (Fig. 2.8f).

- **Thermal noise** comes from the ON-resistance of the switches which is sampled on the sampling capacitors and from the opamp [156].

- **Speed** conversion rate is limited by the opamp's closed-loop configuration, namely, the opamp's finite speed (GBW) and the closed-loop feedback factor [98] (slew rate may also be a limiting factor of the speed).

## 2.2.3 Local Flash Quantizer and Comparators

As the name indicates, this circuit is a quantizer based on the Full-Flash converter topology. In Fig. 2.9a, a generic *N*-bit flash quantizer is shown. It employs, in parallel, a number of comparators,<sup>3</sup> each with their own reference voltage, to be compared with the input signal. The output of each comparator is either 0 or 1, indicating that the input signal's voltage is lower or higher than the reference voltage, respectively. There are various methods of implementing the comparator: cascade of inverters (or simple gain stages), an opamp in open-loop, and the latched comparator [66, 84]. The first two circuits are designed to amplify the input signal or the difference between the input and reference signals to guarantee a logic output (0 or 1, or, in terms of voltage, the negative or positive saturation voltage, respectively). The latched comparator is composed of a pre-amplifier and a positive feedback latch. The pre-amplifier amplifies the small differential input signal and minimizes effects caused by the latch, while the latch guarantees logic levels at the comparator's output.

In Fig. 2.9b, the last block of the 1.5-bit flash quantizer is an XYZ encoder. This circuit is responsible for guaranteeing, depending on the decisions of the comparators, that either X, Y, or Z is one. As mentioned before, these signals decide the B parameter of the reference shifting of the MDAC (see Eq. 2.1). Output bits  $(b_i, b_j)$  are used for digital correction (discussed further on).

The reference voltages may be generated by a resistive or capacitive divider string, or by means of a SC network at the comparators' input. Normally for an N-bit flash quantizer,  $2^N - 1$  comparators are necessary. For a half-bit quantizer (1.5-bit, 2.5-bit, etc.), only  $2^N - 2$  comparators are necessary. N represents the nearest integer greater than the half-bit resolution, e.g., 1.5-bit corresponds to N = 2.

Factors that limit the performance of comparators and, thus, quantizers are given below:

- Offset the opamp and the pre-amplifier introduce an input-referred offset error which may be due to mismatches (between circuit components) or may be inherent to the comparator design [52, 84, 140].

- Charge injection and clock feed-through caused by channel charge and parasitics associated with the sampling switches while turning off [84, 135].

<sup>&</sup>lt;sup>3</sup> The comparator is probably the most widely used component in A/D conversion, fundamental in practically all topologies.

Fig. 2.9 Flash quantizer examples: a Generic N-bit quantizer. b 1.5-bit quantizer

- **Kickback noise** this error occurs during switching in latched comparators. When the comparator goes into latch mode, the high speed of the positive feedback latch causes high speed transients, which inject charge through parasitic capacitors back into the input signal, thus causing unwanted disturbances [52, 84, 140].

- Comparison time this is the time the comparator takes to produce a valid digital output. The worst case scenario is described by an overdrive recovery test, which defines the time the comparator takes to recover from a large input immediately followed by a very small input [104, 140].

- Metastability occurs when a very small input renders the comparator to be unable to produce a valid digital output. This error may be given as a probability of the occurrence of a metastable state [105, 140], as a number of metastable states per second [135], or, for the case of a flash quantizer with various comparators, as the mean time between failures (taking into account the number of comparators) [1].

# 2.2.4 Operational Amplifier and Common-Mode Feedback Circuitry

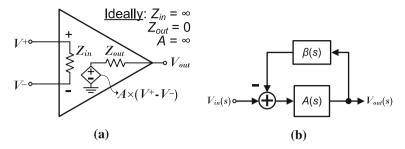

The operational amplifier, better known as opamp, is probably the most important and most used block in analog signal processing. The word operational comes from the fact that these blocks can be used to implement various functional operations. It is an active circuit which ideally has high gain, high input impedance, and low output impedance. Typically working in the voltage domain, a voltage is inputted and an

Fig. 2.10 Opamp: a Basic symbol. b Simplified block diagram of a feedback circuit

amplified voltage is provided at the output, i.e., the opamp is a voltage-controlled voltage source ( $V_{out} = A \times (V^+ - V^-)$ ), where A is the opamp's open-loop gain), as shown in Fig. 2.10a. There are more types of amplifiers, but the one that deserves attention, given the work developed in this book, is the operational transconductance amplifier (OTA). This type of amplifier achieves a high open-loop gain (at low frequencies) at the expense of a high output impedance. They are widely used in SC circuits and do not need low output impedance because they usually only drive pure capacitive loads (and not resistive loads). Their gain and speed depend on the transconductance of specific transistors that compose the OTA.

Opamps usually operate in closed-loop form, inheriting all the associated benefits such as, less sensitivity to circuit and process, supply voltage, and temperature (PVT) variations, thus less distortion, higher input impedance, lower output impedance, and higher bandwidth. Figure 2.10b depicts a simplified block diagram of a negative closed-loop system, where A(s) represents the opamp's open-loop gain (it represents Fig. 2.10a),  $\beta(s)$  is the feedback network (with associated feedback factor), and s is the complex frequency.

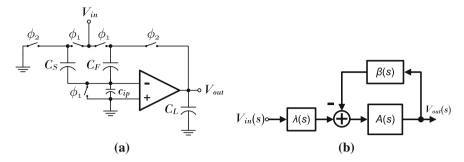

As an example of the functionality and importance of the opamp, the SC circuit of Fig. 2.11a is used (this circuit is similar to Fig. 2.7 for Y = 1). For this example  $C_L$  represents a load capacitor and the objective is to double the input voltage (i.e.,  $V_{out} = 2 V_{in}$ ). During  $\phi_1$ ,  $V_{in}$  is sampled onto  $C_S$  and  $C_F$ . During  $\phi_2$ , the opamp (in closed-loop now) forces a virtual ground at its inverting input and, hence the voltage across  $C_S$  to zero. Due to charge conservation, the charge stored on  $C_S$ ,  $Q_S = C_S V_{in}$ , is transferred to  $C_F$ . No charge goes to the amplifier because of its high input impedance. If  $C_F$  equals  $C_S$  then  $V_{out}$  becomes  $2V_{in}$ . Another way of exemplifying the importance of the opamp is: during  $\phi_1$ , the voltages at the top and bottom plates of  $C_S$  are  $V_{in}$  and zero, respectively. Immediately at the beginning of  $\phi_2$ , the top plate of  $C_S$  is connected to zero, which forces its bottom plate (and the opamp's inverting input) to  $-V_{in}$ . Simultaneously, the opamp (in closed-loop now) forces the virtual ground at its inverting input. In order to accomplish the virtual ground, the output voltage has to be increased by the same amount of voltage, i.e.,  $V_{in}$ . Finally, the output will become  $2V_{in}$  at the end of  $\phi_2$ . If no opamp is used in the aforementioned explanations, neither charge conservation nor virtual ground would

Fig. 2.11 Example using an opamp in a feedback loop: a SC circuit. b Simplified block diagram of the feedback scheme

occur. Consequently, the sampled charge would simply be distributed between  $C_S$ ,  $C_F$ , and  $C_L$ , but  $V_{out}$  would not be  $2V_{in}$  at the end of  $\phi_2$ .

Figure 2.11b illustrates the equivalent block diagram of the SC circuit of Fig. 2.11a, where the feedback network is given by  $\beta(s) = C_F/(C_F + C_S + c_{ip})$  and the input network is  $\lambda(s) = (C_S + C_F)/(C_F + C_S + c_{ip})$  [28].

At the transistor level, many amplifier architectures exist. It will not be the objective of this work to describe any, but rather to give an idea of the common blocks used in most of them. The basic blocks are an input stage (where the input signal is connected), a gain or differential to single-ended conversion stage, and finally, an output driver stage (used to drive the load connected at the output) [66]. It is possible that, besides the input, the output stages be differential, thus inheriting the advantages of fully differential circuits, which will be given further on. When supply voltages were high (higher than 1.8 V in older CMOS technology nodes), gain could be achieved by cascoding (stacking) transistors. In this case enough gain was achieved with a single-stage amplifier, which also has the highest speed of operation. However, due to the power reduction necessity and low supply voltage (1.2 V and lower) tendency of modern nanoscale CMOS technologies (0.13 µm and beyond), it is no longer possible to cascode transistors, therefore, gain can only be achieved by multiple stages, i.e., by cascading stages. Besides gain, the output swing also decreases due to the supply voltage reduction, thus another reason to cascade stages. At this moment, we have arrived at a two-stage amplifier: the first stage mainly for gain and the second for output swing and speed with a small contribution to the overall gain. Due to compensation (to stabilize the amplifier), which is inevitable, the speed of the twostage amplifier is reduced when compared to its single-stage counterpart. If more gain is needed, another stage can be added (three-stage amplifier), at the expense of speed and stability issues.

There are a number of parameters that characterize the performance of opamps. Most of these are limiting factors of their performance. Depending on the application the opamp is inserted in, some become more relevant than others. Here most of them will be described [65, 84, 92, 104, 141]. The parameters are:

- Low-frequency gain: There are two types of gains, differential-mode (DM) and common-mode (CM) gain. Usually an opamp is sized for a given DM gain while minimizing the CM gain. The former is fundamental as it determines the precision of the overall system where the opamp is used (usually in closed-loop). These gains, measured with the opamp in open-loop, are a function of frequency. At low frequencies they are called, the DC gain. An important sub-parameter of gain is its nonlinearity for different output voltages. Normally, for a small output voltage swing, the gain has its maximum value, but for larger voltage swings, the gain tends to be smaller.

- Bandwidth: There are two types of bandwidths, small-signal and large-signal (discussed in the following item), which characterize the high frequency performance of opamps. The former is related to the frequency dependence of the open-loop gain, which is caused by parasitic, compensation, and/or load capacitors present in the opamp. The open-loop gain versus frequency, has a constant value for low frequencies (DC gain, explained before) and then at a certain point in the frequency, the gain starts to decrease or roll-off (at a  $-20\,\mathrm{dB/decade}$  rate). This point is the opamp's bandwidth or the location of the dominant pole. The point at which the gain reaches unity is the unity gain bandwidth ( $f_u$ ) or the gain-bandwidth product (GBW). Note that, GBW =  $f_u$  is only applicable either for a single pole opamp or for an adequately compensated multi-pole opamp [92, 104]. These two design parameters,  $f_u$  and GBW, determine the speed of the system the opamp is inserted in.

- Slew rate or large-signal bandwidth determines the rate at which the opamp can change the output voltage in the presence of large input signals. In large signal conditions, the opamp will try to provide current to charge the capacitors (compensation, load, etc.) of the system. The rate at which it does this is called the slew rate (SR). If the current is insufficient or the opamp does not have enough time (case of SC circuits) to charge the capacitors, the output will not reach the desired value and nonlinear distortion will arise.

- Compensation and Phase Margin: Opamps inserted in feedback loops can be potentially unstable, if not adequately compensated. A measure of this instability is called phase margin (PM). In single-stage opamps (which are less prone to instability), compensation is normally achieved (almost for free) by the load capacitor. In multi-stage opamps (unstable by nature), compensation capacitors and compensation schemes are inevitable.

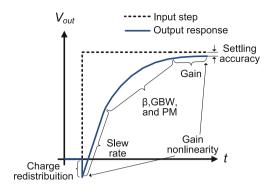

- Settling time: This defines the time it takes the output to reach its final value within a given settling error (associated with the desired accuracy) when a step input is applied. This is probably the most important opamp parameter for SC circuits given that it is a time domain parameter, that includes the effect of gain (and its nonlinearity), small-signal bandwidth, slew rate, phase margin, and the closed-loop's feedback factor. Figure 2.12 [162] depicts an opamp's output response to an input step showing where each mentioned parameter plays its role. If any of them are not designed correctly, their effects will be pronounced in the output response and a longer settling time will probably occur.

Fig. 2.12 Time-domain opamp output response (to an input step) and the role played by some opamp performance parameters

- Output swing is the maximum output voltage range possible that maintains the opamp functioning nominally, i.e., with the desired gain.

- **Common-mode input range** is the maximum input voltage range that guarantees negligible degradation of the opamp's performance.

- **Offset** is the output voltage when the input is zero. Ideally the output voltage should be zero, but will not be due to inherent design issues of the opamp (systematic offset) and mismatches between otherwise matched transistors (random offset). This offset voltage, if large enough, can limit the output swing.

- **Noise** is generated by devices with resistive components such as transistors (resistive channel) and, naturally, resistors. There are many types of noise, the two most commonly discussed are flicker (or 1/f) and thermal noise. The latter is of more importance in high-speed or wideband opamps. Just as in the case of offset, the opamp may be designed for low noise but never for zero noise. Noise determines the smallest detectable input, the opamp may process.

Most parameters can be enhanced by using a fully differential structure for the opamp. In fact, opamp performance can double. This type of structure indicates that the opamp, besides having a differential input, also has a differential output. The advantages of the fully differential architecture are well known and are: larger gain, larger output swing, higher immunity to extrinsic noise, reduced distortion (suppression of even harmonics) and enhanced speed/power ratio [150]. Although the intrinsic noise level of fully differential circuits is higher, the signal-to-noise ratio (SNR) will still be higher than single-ended output circuits due to the larger output swing obtained.

An opamp designed with a fully differential structure needs to employ a special circuit to measure and control its output common-mode voltage. This circuit is known as the common-mode feedback (CMFB) circuit. Without this circuit the uncontrolled output CM voltage could drift to the supply rails. The CMFB circuit guarantees that this voltage stays approximately at midway between the supply rails. There are continuous-time and SC–CMFB circuits. Usually in SC circuits, the SC version of CMFB circuits is preferred.

## 2.2.5 Reference V/I and Buffering

Reference circuits are essential in analog and data converter systems. They generate reference voltages and currents that are used to bias circuits, to compare with other signals, for addition and subtraction operations, among others. In the specific case of data converters, reference circuits are determinant in defining the input and output full-scale ranges. Therefore it is necessary to guarantee a sufficient level of accuracy,<sup>4</sup> so that the overall performance of the data converter is not limited. To achieve this, they need to be independent of external conditions such as, process, supply voltage, temperature, and load disturbances. In the case where a reference voltage needs to drive a large capacitor or various capacitors amounting to a large capacitance (like in DAC circuits), or be used in a high-speed or high-accuracy SC circuit, an additional block needs to be added to the output of the reference circuit. Commonly known as a reference buffer, this block is used to maintain the reference voltage constant and to guarantee that it charges and discharges the capacitors it drives, in the available amount of time (particular case of SC circuits). In other words, the buffer must settle the reference voltage to within a given error, within a given time slot, which depends on the accuracy and speed of the converter.

There are many forms of generating a reference voltage (resistive or capacitive ladders, bandgap circuits, etc.), but this is not the objective of this subsection. Instead, an overview of the issues and difficulties designers have to overcome to buffer and/or stabilize a reference voltage for SC converters, will be given.

It is possible to find many forms of reference voltage schemes in the literature. The options divide into on- and off-chip buffering with (or without) the use of on- and off-chip damping resistors and decoupling capacitors. The following table describes and analyses the most used forms of reference voltage circuitry and buffering schemes.

The conclusions extracted from Table 2.2 can be summarized as follows: the reference circuitry will occupy a large area, will dissipate a large amount of power, and/or will need at least one extra pin. Most of the currently employed solutions suffer from a combination of these drawbacks. From a system-level perspective, neither system-on-chip nor system-in-package designs are benefitted from voltage-domain reference circuitry. To avoid extra costs, no extra pins can be used, therefore, on-chip high-speed buffering must be employed, a trade between cost and power is made. If extra pins are available, then off-chip decoupling may be used (with a low bandwidth buffer), but then a penalty in area is paid for the off-chip decoupling capacitors. All this to avoid on-chip decoupling because silicon area is more expensive (valuable) than discrete components.

<sup>&</sup>lt;sup>4</sup> In [113] it is shown that the reference circuit can have 1-bit lower accuracy than the resolution of the ADC.

| Jes                       |

|---------------------------|

| ۃ                         |

| ğ                         |

| $\mathbf{x}$              |

| ge                        |

| tag                       |

| 7                         |

| >                         |

| $\tilde{s}$               |

| enc                       |

| Ę                         |

| Ē                         |

| ᆵ                         |

| ē                         |

| $\mathbf{e}_{\mathbf{i}}$ |

| 9                         |

| P                         |

| ਰ                         |

| es                        |

| bn                        |

| antag                     |

| 73                        |

| аġ                        |

| .s                        |

| ਰ                         |

| 힏                         |

| ਫ                         |

| es                        |

| age                       |

| antag                     |

| 23                        |

| Вd                        |

| ē                         |

| 무                         |

| $_{\rm ot}$               |

| œ                         |

| ysi                       |

| ੌਰ                        |

| an                        |

| 7                         |

| an                        |

| п                         |

| .2                        |

| ₽.                        |

| 5                         |

| es                        |

| Ă                         |

|                           |

| 2.7                       |

| e,                        |

| Table                     |

| $\mathbf{I}^{\mathbf{a}}$ |

| - '                       |

| <ul> <li>High-speed buffer with wide bandwidth.</li> <li>High power consumption.</li> <li>Noise performance hard to achieve (as frequency rises, buffer output impedance rises).</li> <li>181 uses a deglitch circuit to minimize glitches during switching.</li> <li>Wirebond inductance too large current peaks, the buffer may require dedicated supply pins.</li> <li>Wirebond inductance too large or current peaks, the buffer may require dedicated supply pins.</li> <li>Wirebond inductance too large for off-chip decoupling due to impractical amount of ringing on reference voltage.</li> <li>Large on-chip capacitors, occupying large area, are mavoidable [20].</li> <li>On-chip RC filter [34].</li> </ul> | Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Diagram                                             |                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------|

| off-chip ← → on-chip Free Pad/Pin Ref. circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <ul> <li>High-speed but bandwidth.</li> <li>High power cor</li> <li>Noise perform achieve (as five buffer output rises).</li> <li>[81] uses a d to minimize g switching.</li> <li>Due to large cur buffer may req supply pins.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | off-chip ← → on-chig<br>Free Pad/Pin Ref.           | Accuracy +  Power -  Speed +  On-chip area +  Off-chip area + |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Wirebond inductor for off-chip decimpractical amount reference with the company of the comp | off-chip← → on-chip<br>Free Pad/Pin C <sub>im</sub> | Accuracy +  Power +  Speed +  On-chip area -  Off-chip area + |

|                       | Performance | • Accuracy +- • Power + • Speed - • On-chip area +- • Off-chip area                                                                                                                                                                                                                                                                                                                                                                                       | • Accuracy +- • Power + • Speed - • On-chip area + • Off-chip area -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (Continued) |

|-----------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|                       | Diagram     | $\begin{array}{c} \text{off-chip} \longleftarrow \\ \text{Wirebond} \\ \\ C_{cw} \\ \\ C >> \end{array}$                                                                                                                                                                                                                                                                                                                                                  | off-chip $\leftarrow$ $\rightarrow$ on-chip $\stackrel{R}{\leftarrow}$ $\stackrel{Ref.}{\leftarrow}$ $\stackrel{Ref.}$ |             |

|                       | Analysis    | <ul> <li>Low bandwidth buffer.</li> <li>Low power consumption.</li> <li>Noise performance and output impedance dependent on quality (ESL and ESR) of decoupling capacitors.</li> <li>Wirebond inductance causes ringing of the internally generated reference voltage. Dampen ringing with large on-chip capacitors and resistors (these occupy large area).</li> <li>Reduce inductance with special packaging [69].</li> <li>Additional pins.</li> </ul> | <ul> <li>Reference is taken off-chip, RC filtered and dampened and brought on-chip again.</li> <li>Two wirebonds in reference voltage path.</li> <li>Special packaging unavoidable.</li> <li>Two additional pins.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |

| Table 2.2 (Continued) | Description | On-chip buffer with external decoupling [22, 31, 69, 109, 155]                                                                                                                                                                                                                                                                                                                                                                                            | On-chip reference without buffer with external decoupling [68]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

| Table 2.2 (Continued)                                      |                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                  |                                                                   |

|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Description                                                | Analysis                                                                                                                                                                                                                                                                                 | Diagram                                                                                                                                                                          | Performance                                                       |

| On-chip buffer with external and internal decoupling [117] | <ul> <li>Use of external and internal capacitors and damping resistors.</li> <li>Special internal decoupling scheme (low-V<sub>T</sub> decoupling capacitors) [117].</li> <li>Additional pins.</li> </ul>                                                                                | off-chip $\leftarrow$ on-chip $C_{cvt}$ $C_{cvt}$ $C_{cvt}$ $C_{cvt}$ $C_{cvt}$ $C_{cvt}$ $C_{cvt}$                                                                              | • Accuracy +- • Power + • Speed +- • On-chip area • Off-chip area |

| Off-chip reference with internal decoupling [21, 88, 171]  | <ul> <li>Use large on-chip capacitors to dampen the ringing caused by wirebond (occupying large area).</li> <li>Internal decoupling capacitor may be larger than converter itself [171].</li> <li>For lower inductance more pins must be used [21].</li> <li>Additional pins.</li> </ul> | $\begin{array}{c} \text{off-chip} \longleftarrow \longrightarrow \text{on-chip} \\ \\ \text{Ref.} \\ \\ \text{circuit} \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$ | Accuracy — Power + Speed — On-chip area — Off-chip area —         |

Special packaging: chip-scale flip-chip with  $< 0.2\,\mathrm{nH}$  wirebond inductances

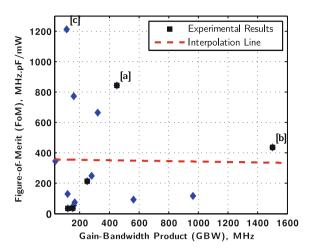

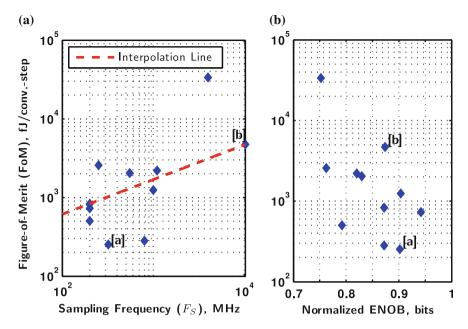

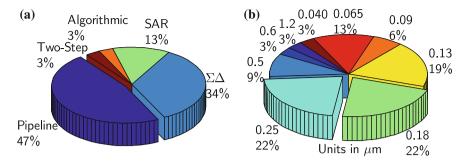

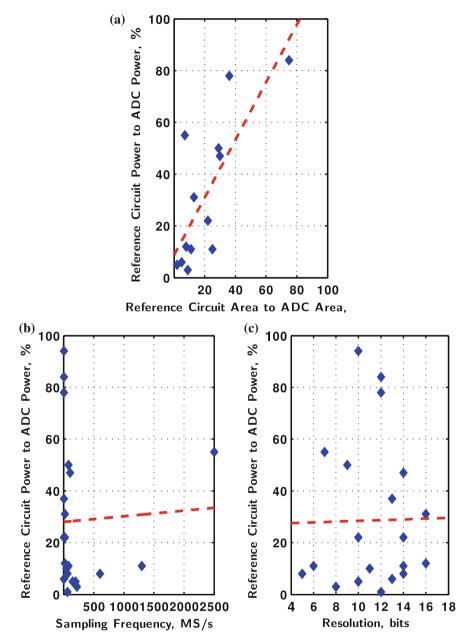

Parameters of reference circuits and buffers that may affect the overall performance of data converters are given next. They are: